拉通理解嵌入式是什么?单片机是什么?cpu内核是什么?CPU架构是什么?它们的关系是什么?

拉通理解嵌入式是什么?单片机是什么?cpu内核是什么?CPU架构是什么?它们的关系是什么?

嵌入式是什么?

嵌入式系统:嵌入式是以应用为中心,以计算机技术为基础,软件硬件可裁剪,适用于对功能、可靠性、成本、体积、功耗有严格要求的专用计算机系统。

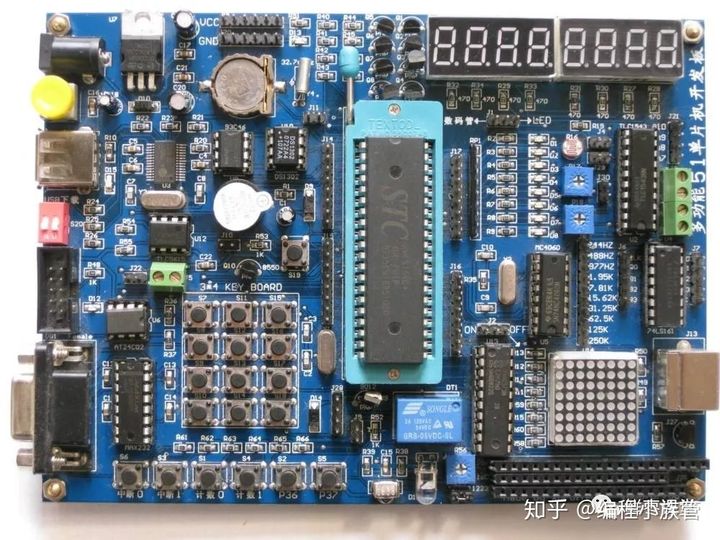

一个嵌入式系统的典型架构如下:

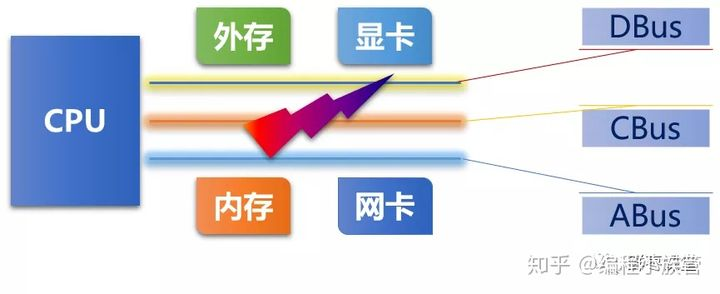

硬件角度来看,嵌入式系统就是以处理器(CPU)为核心,依靠总线(Bus)进行连接的多模块系统:

单片机是什么?

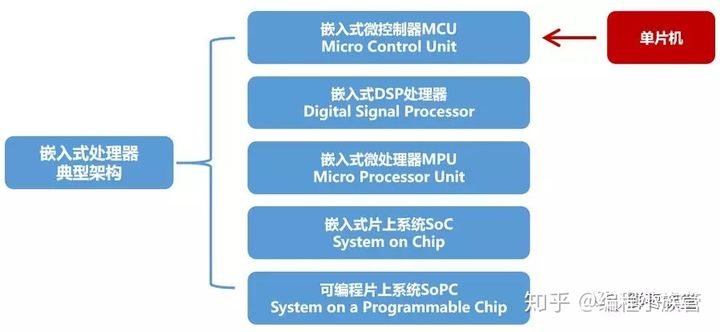

嵌入式系统的核心,就是嵌入式处理器。嵌入式处理器一般分为以下几种典型类型:

- 嵌入式微控制器MCU(Micro Control Unit)

MCU内部集成ROM/RAM、总线逻辑、定时/计数器、看门狗、I/O、串口、A/D、D/A、FLASH等。典型代表是8051、8096、C8051F等。

- 嵌入式DSP处理器(Digital Signal Processor)

DSP处理器专门用于信号处理,在系统结构和指令算法进行了特殊设计。在数字滤波、FFT、频谱分析中广泛应用。典型代表是TI(德州仪器)公司的TMS320C2000/C5000系列。

- 嵌入式微处理器MPU(Micro Processor Unit)

MPU由通用处理器演变而来,具有较高的性能,拥有丰富的外围部件接口。典型代表是AM186/88、386EX、SC-400、PowerPC、MIPS、ARM系列等。

- 片上系统SoC、SoPC

还有嵌入式片上系统SoC(System on Chip)和可编程片上系统SoPC(System on a Programmable Chip)。

单片机是什么:单片机就属于上述的第一种—MCU(嵌入式微控制器)。

单片机,又称为单片微控制器,英文叫Single-Chip Microcomputer

它其实就是一种集成电路芯片,是通过超大规模集成电路技术,将CPU、RAM、ROM、输入输出和中断系统、定时器/计数器等功能,塞进一块硅片上,变成一个超小型的计算机。这么说来,单片机不就是一个嵌入式系统?

“单片机”其实是一种古老的叫法。以前半导体工艺技术不成熟,不同的功能无法做进一个芯片(Chip),所以会有多片机。现在半导体技术早已非常发达,所以不存在多片机。但是,“单片机”的叫法却一直延用至今。

很多高校老师喜欢强调单片机姓“单”,除了指单片机只是一个硅片之外,更多是指单片机的功能单一,它是完成运算、逻辑控制、通信等功能的单一模块。即便它性能再强大,功能依然是单一的。

嵌入式和单片机的区别

嵌入式系统是一个大类,单片机是其中一个重要的子类。嵌入式系统像是一个完整的计算机,而单片机更像是一个没有外设的计算机。

以前单片机包括的东西并不算多,两者的硬件区别较为明显。但是,随着半导体技术的突飞猛进,现在各种硬件功能都能被做进单片机之中。所以,嵌入式系统和单片机之间的硬件区别越来越小,分界线也越来越模糊。

于是,人们倾向于在软件上进行区分。

从软件上,行业里经常把芯片中不带MMU(memory management unit,内存管理单元)从而不支持虚拟地址,只能裸奔或运行RTOS(实时操作系统,例如ucos、华为LiteOS、RT-Thread、freertos等)的system,叫做单片机(如STM32、NXP LPC系列、NXP imxRT1052系列等)。

而把芯片自带MMU可以支持虚拟地址,能够跑Linux、Vxworks、WinCE、Android这样的“高级”操作系统的system,叫做嵌入式。

CPU内核是什么?

一颗单片机由中央处理单元(CPU)、程序存储器(ROM)、数据存储器(RAM)、周边外设(Peripheral)、及程序数据总线(BUS)等单元组成。

在单片机发展的过程中,出现过很多的中央处理单元设计,俗称CPU内核,例如Zilog的Z80内核、Intel的8051内核、Microchip的PIC16、18、dsPIC、PIC32内核、Motorola的68000内核、Atmel的AVR内核、ARM的Cortex M0,M3,M4等内核,还有很多,数不胜数。

绝大多数CPU都采用了一种翻转内核的封装形式,也就是说平时核心(Die)又称为内核,CPU中心那块隆起的芯片就是核心,是由单晶硅以一定的生产工艺制造出来的,CPU所有的计算、接受/存储命令、处理数据都由核心执行。

各种CPU核心都具有固定的逻辑结构,一级缓存、二级缓存、执行单元、指令级单元和总线接口等逻辑单元都会有科学的布局。

CPU架构是什么?

这个问题没太搞懂,笔者大致理解有两个维度的架构,出发点不同,理解不同:

- 厂商产品系列的维度:

CPU架构又称处理器架构(Processorarchitecture)是CPU厂商给属于同一系列的CPU产品定的一个规范,主要目的是为了区分不同类型CPU的重要标示。

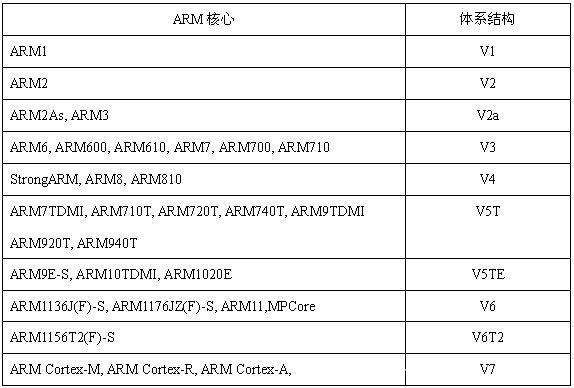

比如展示的ARM架构和核心对应关系,这里的架构就是这个维度上说的架构。

题外话:目前市面上的CPU指令集分类主要分有两大阵营,一个是intel、AMD为首的复杂指令集CPU,另一个是以IBM、ARM为首的精简指令集CPU。两个不同品牌的CPU,其产品的架构也不相同。

- 根据cpu核心的设计实现把市面上核心的设计大致分类:

-

HARVARD(哈佛)架构:ROM(程序空间)与RAM(数据空间)分开,便于程序与数据的同时访问,减少程序运行时访问的瓶颈,提高数据吞吐。

-

PRINCETON(普林斯顿)架构:采用通用计算机广泛使用的ROMRAM合二为一的方式,就是众所周知的冯诺依曼结构,程序指令存储地址和数据指令存储地址指向同一存储器不同位置,因此程序指令和数据的宽度相同。

举例说明,以英特尔为例,MCS-51用的是哈佛架构,而后及产品16位的MCS-96就是普林斯顿架构,ARM公司卖的内核几乎多是哈佛架构的。

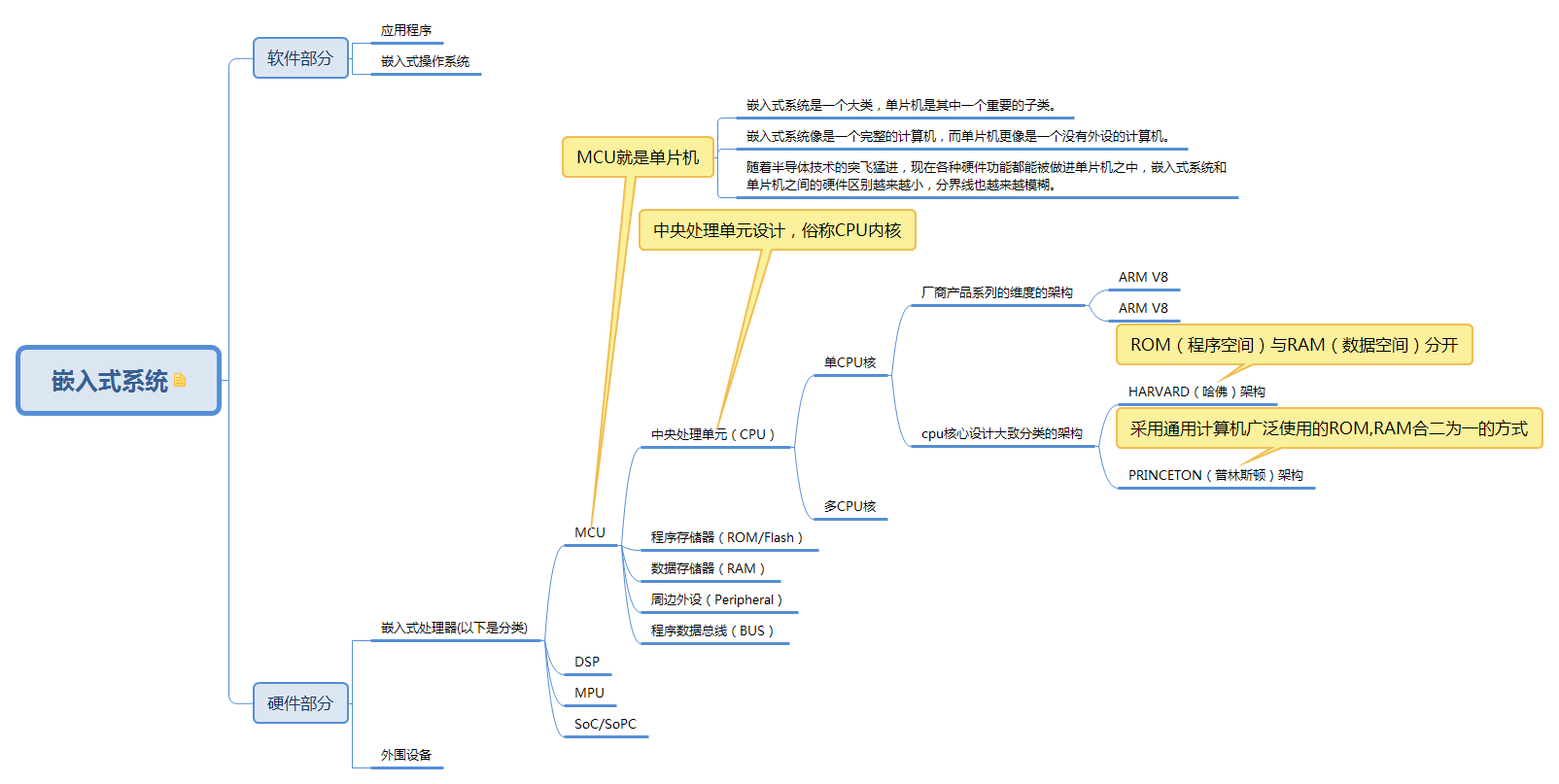

嵌入式、单片机、cpu内核、cpu架构的关系是什么?

笔者根据整理的上述材料,大概画了一个思维导图,以表示嵌入式、单片机、cpu内核、cpu架构之间的关系:

注:其中嵌入式系统和单片机的区别界限,越来越模糊了!

本文摘自或参考: